### Hochschule für Technik, Wirtschaft und Kultur Leipzig

Fakultät Informatik, Mathematik und Naturwissenschaften Master Computer Science

Masterthesis to Earn the Grade

Master of Science (M.Sc.)

# Evaluation of Intel Trusted Execution Technology for Use in a Partitioning Hypervisor

A Trusted Jailhouse

Submitted by: Benjamin Block Matriculation Number: 57646

Munich February 12, 2015

Supervisors: Prof. Dr. rer. nat. Klaus Bastian

Dipl.-Ing. Jan Kiszka

# **Abstract**

Modern hardware virtualization techniques on the x86 architecture make it possible to construct effective hypervisors with only a small necessary code base. Hypervisors like Jailhouse use this to provide safe segregation of the platform's hardware resources into distinct partitions. Using the guarantees given by the hardware and the small, verifiable code base of the hypervisor makes it possible to run tasks with mixed criticality together on the same hardware platform, put together with only commodity hardware.

Crucial for this function, and with that for the function of potentially safety relevant tasks, is that the hypervisor is started correctly, with the correct hypervisor-image, the correct configuration and on the actual hardware which provides the guarantees.

In this work, Intel's Trusted Execution Technologies, also shortened with TXT, are evaluated for the task to launch such a hypervisor during the runtime of a general purpose operating system. To prove this concept, a design to support TXT was created and subsequently implemented with the hypervisor Jailhouse as base. It is now possible to launch Jailhouse via TXT, and thereafter to verify its integrity with proven methods like remote attestation. Although this improves the confidence in the hypervisor setup considerably, it also became clear that TXT has a large amount of intrusive requirements, which it will force upon every software that wants to make use of it. It only becomes a valid option to use TXT in the envisioned use case, if these requirements are acceptable.

# **Eidesstattliche Versicherung**

Ich erkläre hiermit, dass ich diese Masterarbeit selbstständig ohne Hilfe Dritter und ohne Benutzung anderer als der angegebenen Quellen und Hilfsmittel verfasst habe. Alle den benutzten Quellen wörtlich oder sinngemäß entnommenen Stellen sind als solche einzeln kenntlich gemacht.

Diese Arbeit ist bislang keiner anderen Prüfungsbehörde vorgelegt und auch nicht veröffentlicht worden.

Ich bin mir bewusst, dass eine falsche Erklärung rechtliche Folgen haben wird.

Benjamin Block, München, February 12, 2015

# **Contents**

| 1 | Gaiı | ning Trust in a Hypervisor                                         | 1  |

|---|------|--------------------------------------------------------------------|----|

|   | 1.1  | Structure of this Work                                             | 3  |

| 2 | Virt | ualization of Hardware                                             | 5  |

|   | 2.1  | The Use of Virtual Machine Monitors                                | 5  |

|   |      | 2.1.1 Definitions                                                  | 5  |

|   | 2.2  | Hardware Support for Virtualization on x86                         | 7  |

|   |      | 2.2.1 CPU-Virtualization                                           | 8  |

|   |      | 2.2.2 Virtualizing Device I/O                                      | 12 |

|   | 2.3  | The Jailhouse Hypervisor                                           | 15 |

|   |      | 2.3.1 Running Jailhouse on Linux                                   | 19 |

| 3 | Trus | sted Execution                                                     | 25 |

|   | 3.1  | Overview of the Envisioned Execution                               | 26 |

|   | 3.2  | Establishing Trust in Software                                     | 27 |

|   | 3.3  | The Trusted Platform Module                                        | 32 |

|   |      | 3.3.1 Functional Overview                                          | 34 |

|   | 3.4  | Intel's Trusted Execution Technologies                             | 40 |

|   |      | 3.4.1 Overview                                                     | 41 |

|   |      | 3.4.2 Intel's Safe Mode Extension                                  | 42 |

|   |      | 3.4.3 Controlling the Launch of Software with the DRTM             | 48 |

| 4 | Rela | ated Work                                                          | 53 |

|   | 4.1  | Trusted Boot with TBoot                                            | 53 |

|   | 4.2  | Running Small Applications in a Trusted Environment with Flicker . | 55 |

|   | 4.3  | TrustVisor: a Hypervisor for Minimizing Application's TCB          | 57 |

|   | 4.4  | Other Works                                                        | 58 |

| 5 | Des  | ign of the Trusted Hypervisor Execution                            | 61 |

|   | 5 1  | Design Overview                                                    | 62 |

| Αŗ | pend | ix                                                    | 121   |

|----|------|-------------------------------------------------------|-------|

| 9  | Con  | clusion                                               | 119   |

| 8  | Futu | re Work                                               | 117   |

|    |      | 7.5.2 System Management Mode                          | . 114 |

|    |      | 7.5.1 No Trust from Within the Launched System        |       |

|    | 7.5  | Known Limitations                                     | . 113 |

|    |      | 7.4.3 Attacks Against the Measured Launch Environment | . 112 |

|    |      | 7.4.2 Attacks Against the Measured Launch             | . 111 |

|    |      | 7.4.1 Software Attacks Prior to the Measured Launch   | . 108 |

|    | 7.4  | Software failures and attacks                         | . 108 |

|    |      | <u> </u>                                              | . 107 |

|    |      | 7.3.3 Attacks via Power Management                    |       |

|    |      | 7.3.2 Change of Firmware Settings                     |       |

|    | 1.0  | 7.3.1 Malicious DMA Devices                           |       |

|    | 7.3  | Hardware-Based Attacks                                |       |

|    | 7.2  | The Attacker Profile                                  |       |

| •  | 7.1  | Assumptions About the Analysed System                 |       |

| 7  | Seci | rity of the Trusted Hypervisor                        | 101   |

|    | 6.8  | Performance                                           | . 97  |

|    | 6.7  | Code Size                                             | . 95  |

|    |      | 6.6.2 Different Processor IDs                         | . 95  |

|    |      | 6.6.1 Fixing the MLE Image                            | . 94  |

|    | 6.6  | Open Issues and Constraints                           |       |

|    | 6.5  | Changes Made to the Jailhouse Hypervisor              |       |

|    | 6.4  | Implementation of the TXT Stub                        |       |

|    | 6.3  | Implementation of the TXT Loader                      |       |

|    | 6.2  | Build of the Hypervisor Image                         |       |

| U  | 6.1  | Programming of the TXT Components of the System       |       |

| 6  | The  | TXT Implementation for Jailhouse                      | 75    |

|    | 5.5  | Changes in Jailhouse                                  |       |

|    | 5.4  | Responsibilities of the TXT Stub                      |       |

|    | 5.3  | Responsibilities of the TXT Loader                    |       |

|    | J    | 5.2.1 Structure of the TXT Stub                       |       |

|    | 5.2  | Defining the Parts of the Hypervisor's MLE            | . 64  |

| Co | ontents                                 | Benjamin Block |

|----|-----------------------------------------|----------------|

| Α  | Implementing VMMs with Trap and Emulate | 121            |

| В  | List of Figures                         | 125            |

| C  | Nomenclature                            | 129            |

| D  | Bibliography                            | 135            |

# 1 Gaining Trust in a Hypervisor

Virtualization solutions which execute multiple operating systems (or in general, bare metal applications) on top of and alongside with other software are today widely used in computer systems for a variety of tasks [WP10, Gol74]. They serve, for example, to support development and to test of new software — not least to develop and test operating systems [Bin06]. Virtualization is also used to raise efficiency in data centers by running more than one system on real hardware, and thus it lowers the time this hardware spends in idle [KNS13]. In doing so, those solutions also guarantee that the virtualized systems are isolated from each other, so that they can't access each other's information or worse, influence each other maliciously [BM13].

But until some years ago, it was not possible to develop such solutions in a way to allow them to execute the virtualized software (virtual machines, abbr. VM) unchanged and directly on processors of the x86 architecture. This was largely due to some operations that would, when executed natively on the processor, expose systems states without the ability to trap them, or they would fail silently without generating errors, and thus they would fail the isolation [NSL+06]. Softwares like Xen or VMware had to deploy other solutions to make the virtualization possible [AA06, BDF+03, BDR+12].

They also had to develop ways to make it possible for the VMs to use I/O devices. While some decided to fully emulate I/O, and thus also made it possible to multiplex existing devices, others had to spend this unwanted effort to uphold the isolation [AJM<sup>+</sup>06].

All this overhead meant that the performance of the virtual machines would suffer [ByMK $^+$ 06]. This lead to the implementation of extensions for the x86 architecture by both Intel and AMD [NSL $^+$ 06, Kle09, AMD05] — Intel named their extension VT-x and AMD theirs SVM. They allow the virtual machine monitors (the part of the virtualization solutions that creates and maintains the environment

for the virtual machines, abbr. VMM, also called Hypervisor) to let the virtualized software run directly on the processor. Any operation that would change an important system state or leak inappropriate information can now be trapped and handled correctly by the VMM. Further introductions of additional memory management units between I/O devices and their connection to the main memory via DMA (IOMMUs) have made it possible for VMMs to let virtual machines use these devices directly as well [AJM<sup>+</sup>06].

To use these extensions, the VMM has to have sufficient privileges, it has to be executed with privilege level 0 (often also referred to as ring 0) [AMD05, Int14b]. Even more, once the system activates the extensions, the VMM can overrule any other piece of software — including the operating system that may have been executed before the activation [Sin14a]. This means that every software which is executed thereafter on top of it — possibly multiple complete operating systems, together with their own software stack — has to rely on the proper function of the VMM.

This provides the motivation for this work. The first step in ensuring that the VMM — or any other piece of software — executes properly, is to make sure, before executing it, that the loaded code with all its inputs is the expected. The same problem can already be seen in the execution of operating systems and a software stack on top of them — correct execution relies on the proper function of the OS. Along with this task comes the next problem: how can a third party be convinced — may it be the user of the system or any other computer — that the correct software was started and is still running? It can't trust any results or commands from this software or, in case of a VMM, any of the VMMs without this knowledge.

This is exactly the problem that the Trusted Execution Technology from Intel (abbr. Intel TXT) tries to solve [Gre13, Int14c]. TXT was introduced by Intel in 2007 and adds new instructions to x86 to support the trusted execution of arbitrary software, at any point during the lifetime of a system — not limited to either VMMs or OSs. To support its task, it makes heavy use of the Trusted Platform Module (abbr. TPM [CYC+08, Cor10]) to securely save information and to provide the ability to attest that the expected software was executed.

Currently TXT is only used in few software systems, most of them use it in the context of *secure boot* (as *replacement* for the same functionality provided by UEFI). They activate it as part of the boot process to record and test the code of the OS or VMM that is about to be started on the bare metal [FG13].

This work will evaluate it as means to start a VMM during the lifetime of an already

running OS. In the presented scenario, the OS needs to be kept unimpaired, and will continue to execute as one of the started VMM's virtual machines. A design and implementation, confirming to these requirements, has been created with the hypervisor Jailhouse [Jaib, Kis14] and the operating system Linux. This work will present both the design and implementation, and a throughout analysis of what Jailhouse can guarantee by using Intel TXT to start. Furthermore, it will show how a user can gain trust in the system once it is started, and what impact the additional work for using TXT has on the hypervisor.

#### 1.1 Structure of this Work

The following chapters of this thesis are organized in the following way. Chapter 2 on page 5 will give a more in-depth introduction into the topic virtualization; it will define the problems VMMs face and how recent hardware extensions on x86 improved that situation; finally, it will present the VMM used as example in this work: Jailhouse. Chapter 3 on page 25 will then present the motivation as to why Intel TXT is considered to be used to start Jailhouse, and how exactly TXT works as hardware extension. After establishing these fundamentals, Chapter 4 on page 53 will elaborate on what others have done in this area. Thereafter, Chapter 5 on page 61 will present the design developed to solve the task of this work. Chapter 6 on page 75 will then present the implementation created according to this design, together with measurements about its size and performance. In Chapter 7 on page 101, the design and implementation will be evaluated for their security: against what malicious attacks can they defend themselves by using TXT in the way proposed. The final two chapters, 8 on page 117 and 9 on page 119, will discuss what future work in this field is still necessary and conclude the results that could be made during this work.

# 2 Virtualization of Hardware

This chapter will present the necessary fundamentals to understand how the virtualization solution Jailhouse works. Jailhouse will be used as the main example in this work, and thus also sets a large share of the requirements for the design and implementation created with it. Apart from this, parts of the shown techniques will later also be used as means in the security analysis to accomplish certain properties.

The first Section 2.1 will define what this work understands under the broad term of virtualization and what requirements this poses for a solution aiming to implement this concept. How these requirements can be fulfilled with recent architecture extensions to x86 will be presented in Section 2.2 on page 7. Finally, Section 2.3 on page 15 will give an in-depth overview of the main hypervisor example in this work: Jailhouse. It will show how Jailhouse is different from other solutions, how it handles the virtualization of the system and with that, what requirements it imposes on a design and implementation of Intel TXT for it.

## 2.1 The Use of Virtual Machine Monitors

#### 2.1.1 Definitions

Virtualization in computing is a very broad term, used for a variety of topics. This work will use the following as the general definition for the term [Sin04]:

**Definition 2.1.** *Virtualization* is a framework or methodology of dividing the resources of a computer into multiple execution environments, by applying one or more concepts or technologies such as hardware and software partitioning, timesharing, partial or complete machine simulation, emulation, quality of service, or others.

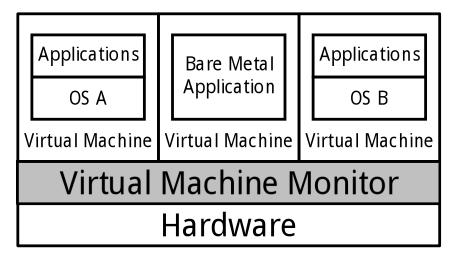

FIGURE 2.1: Organization of virtual machines on top of a VMM virtualizing the complete hardware of computer system.

This methodology is frequently applied to different resources of a single computer, such as memory, the processor or I/O devices; most commonly by the operating system running directly on the hardware. This makes it possible to run more than one application on top of it, without the need for these applications to know of each other or the limitations of the actual hardware. This requires that the operating system has full access to the actual hardware [TB14].

What this work uses the term virtualization for, is to create a virtual version of a whole computer, so that it becomes possible to run multiple operating systems — or more generally, applications that assume direct hardware control (bare metal applications) — next to each other, each on their own virtual version of the system. One such virtual instance of the system is commonly called a virtual machine (abbr. VM) and was formally specified in 1974 by Popek and Goldberg [PG74].

The software used to manage the different virtual machines on one computer is called the *virtual machine monitor* or *hypervisor*; an example of how such a system can be organized is shown in Figure 2.1. Popek and Goldberg defined a VMM as follows:

**Definition 2.2.** A software system is considered a *virtual machine monitor* if it has the following characteristics:

- 1. Fidelity: The VMM provides software running on it an environment essentially identical with the original machine.

- 2. Performance: The software running in this environment shows at worst only minor decreases in speed.

3. *Control*: The VMM is in complete control of all the hardware resources of the underlaying computer system.

By requiring an "essentially identical" environment, it is left open that there may be differences in timing and system resources available to the virtual machine. Both stem from the fact that the original system is shared between multiple virtual machines and thus can't provide the same resources as if it was used directly. For example, there will be less memory and processor time available for a single VM.

To achieve the second characteristic about performance, it is necessary to run most of the instructions of the VM directly on the real processor. A VMM that would uses an interpreter to execute the instructions may have to use hundreds of physical instructions for the interpretation of just one instruction of its VMs [AA06]. This rules out the use of an emulator.

The final characteristic makes sure that VMs can only ever use resources explicitly allocated to them — even more, the VMM has to have the ability to recover any resource from a VM, if that is necessary. This also means, any access to another VM's resources which are not explicitly shared has to be suppressed by the VMM, and thus makes it possible to isolate them from each other.

**Implementation approach** The classic implementation approach for a VMM to fulfill those characteristics is *Trap and Emulate*.

A more comprehensive description of this approach, and why until recently it was **not** possible on x86 to implement it directly, can be read in Appendix A on page 121. VMMs did exist, but they had to use more complex and slower algorithms [VMw09, BDR<sup>+</sup>12]. This situation only just changed with the introduction of the extensions described in the following section.

# 2.2 Hardware Support for Virtualization on x86

To make it possible on x86 to implement efficient VMMs, with only a small amount of source code (compared to the solutions made before), both Intel [NSL+06, Int14b] and AMD [AMD05] released extensions for their x86 architectures to support the original trap-and-emulate approach. This section gives a short overview of how Intel solved the problem with their extension VT-x (AMD works conceptional in the same way, but is differently implemented and thus incompatible).

#### 2.2.1 CPU-Virtualization

Essentially, VT-x introduces two new forms of operations to the x86 architecture: VMX root operations and VMX non-root operations (VMX stands for Virtual Machine eXtensions). VMX root operations are very much like operations without the extension. The only differences are, once activated, root operations have access to a new set of instructions (the VMX instructions) and certain control registers become become limited (some bits in CRO and CR4 become fixed). These operations are intended to be used by the VMM [Int14b].

The VMX non-root operations are intended to be used by the VMs, or *guests* as they are also commonly called. They also behave much like the normal x86 instructions. It is, for example, possible to operate under all four privilege levels with them. But they add the ability for the VMM to trap all sensitive instructions executed by the guest — such a trap is called *VM exit*.

**Trap-and-Emulate using VT-x** To enter these new operation modes, the VMM has to execute the instruction *VMXON*. It then executes with the new VMX root operations and has access to the new instruction to setup and configure its guests. Subsequently, it can decide to enter a guest by doing a *VM entry*. This will set the processor into the VMX non-root operation mode and then continue the execution in the guest as long as no *exit reason* is reached — a trap for example. Figure 2.2 on the next page illustrates this life cycle based on a VMM with two different guests.

The transition between root- and non-root is controlled by a structure called the *Virtual-Machine Control Structure* (abbr. *VMCS*; this acts as a shadow structures in the trap-and-emulate scheme). It includes an area controlling the state of the guest upon a VM entry (the *guest-state area*), an area specifying the state that is restored when a VM exit occurs (the *host-state area*) and finally some control fields to configure when and why a VM exit shall happen (the *VM-Execution Control Fields*).

Figure 2.2 on the facing page also shows how this structure is used during the life cycle of a VMM. After the VMM has executed VMXON and entered the root operations, it will configure the VMCS by using the new instructions that have been added for this (VMCLEAR, VMPTRLD, VMREAD and VMWRITE). It writes its own processor state into the host area, and the state of the guest into the guest area. This includes all crucial operation state information of the processor, such as:

## VMX Non-Root Operations trap Guest 0 Guest 1 VMCS 0 VMCS<sub>1</sub> Guest-State load **Guest-State** Area Area VM VM Exit VM Exit Entry VM Mon **VMXON VMXOFF VMCS 0/1** oad Host-State Area VMX Root Operations

# FIGURE 2.2: Diagram showing the life cycle of a virtual machine monitor using the VT-x extension. Each combination of VMM and guest has its own VMCS, with its own set execution elds; the host-state area has to be shared manually between them.

- control registers,

- segmentation registers,

- some model specific registers (MSRs; for example the MSR EFER),

- important execution registers, like the instruction pointer,

- and the descriptor registers.

Next to these states, the VMM also specifies what later shall cause a VM exit. Again, this list is made up from several components, the most important include:

- execution of several different sensitive instructions,

- interrupts during the guest-execution,

- accesses of sensitive processor registers,

• I/O via the port I/O mechanism and others.

Most of these exit-reasons can also be specified more precisely than only on the base of the whole class of operations (which would be the case in the classic trap-and-emulate scheme). It is, for example, possible to enumerate the exact I/O ports a guest can access uninterrupted via port I/O, and which others will cause a VM exit. This way it is possible to allocate resources to a VM without the need to intervene later — saving VM exits, which are quite costly [FO06].

When this is done, the VMM can activate the configured guest via the instruction VMLAUNCH. This instruction won't return on success, it will instead load the specified states from the guest state area and the processor will continue executing in the non-root operation mode, until one of the exit-reasons is met.

Lastly, once such an exit-reason is met, the processor will proceed with a VM exit and reload the states saved in the host area of the VMCS and return to the VMM. It can then examine the exact reason and emulate the effect appropriately, like in the classic trap-and-emulate scheme. This process is continued for the whole life-cycle of the VMM and ultimately turned off by a call of VMXOFF.

Memory Tracing using Extended Page-Tables Although this would already meet Popek and Goldberg's theorem (A.1 on page 122) [NSL+06] and remove the need for implementing a complex binary transformation engine inside the VMM, it was found that it would not add much performance advantage to a VMM using it [AA06]. The main reason for this was the need to still implement a page level memory tracing (described in A on page 122). This meant that every access to a critical memory area in a guest (e.g.: page tables or MMIO areas) had to be trapped and would cause a VM exit; this added a considerably large overhead to the execution [VMw09].

This shortcoming was again addressed by both Intel and AMD [AMD08]. Intel's implementation is called  $Extended\ Page\ Tables$  (abbr. EPT). The more general term, which addresses both implementations, is  $Second\ Level\ Address\ Translation$  (abbr. SLAT). It extends the paging algorithm used during VMX non-root operations with an additional address translation step.

Usually, when paging is activated, addresses are translated two times: the addresses used in the software are *virtual addresses* and are translated into *linear addresses* using the segmentation mechanism of the protected mode (although today, virtual addresses are usually resolved into the same linear addresses to remove complexity and because segmentation is only partially supported by x86\_64); these are then

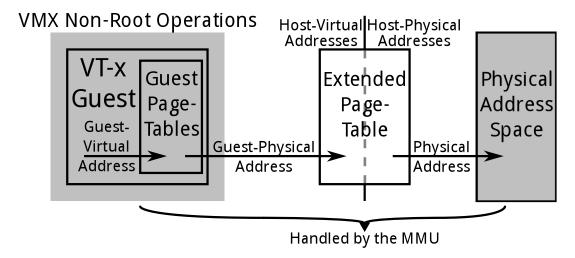

FIGURE 2.3: Diagram showing the resolution of a virtual address of a VT-x guest into a physical address of the host using the extended page tables.

translated again using the activated page-table and thus resolve into the final *physical address* [Int14b].

This process is depictured in Figure 2.3. Both translations, the one from guest-virtual into guest-physical addresses and then the one into host-physical addresses, are handled by the hardware memory management unit (abbr. MMU). The EPT itself is assembled during the configuration of the guest or later on demand by the VMM. It can not be accessed by the guest during the non-root operations — it is completely transparent to the guest; it just programs the paging as it would running directly on the hardware. Because the VMM can exactly choose which physical resources it wants to allocate for the guest, it has no longer any need to intervene later on when the guest is executed, and thus it can completely remove the memory tracing and traps for accesses to the page-configuration registers.

Further extensions to VT-x (the *Unrestricted Guest Mode*) made it even possible for guests to run completely without paging, in the *real*- or *unpaged protected- mode*. During those, the EPT is still enabled and the MMU still translates every memory reference done by the guest, but the guest itself does not have to employ any translation scheme. Hence, the control characteristic is still satisfied, but the VMM can deactivate even more traps and thus has to handle even fewer VM exits.

## 2.2.2 Virtualizing Device I/O

Another difficult problem for VMMs on x86 is to maintain the control characteristics for device I/O [WRC08, WSC<sup>+</sup>07, AJM<sup>+</sup>06]. By using VT-x in combination with an EPT, it is possible to safely allocate I/O ports and MMIO regions directly to a single VM. I/O ports are handled as described in 2.2.1 on page 8 and MMIO regions by enabling the SLAT — a VM may only access a MMIO region that is mapped into its guest-physical space.

But devices usually also deploy some form of DMA to save processor time, they read and write data directly into the main memory. These accesses are not managed by the processor's MMU, and therefore they are also not affected in any way by the SLAT or any other paging deployed by the processor. Guests could abuse this by programming the assigned devices with wrong physical addresses — violating the control characteristic.

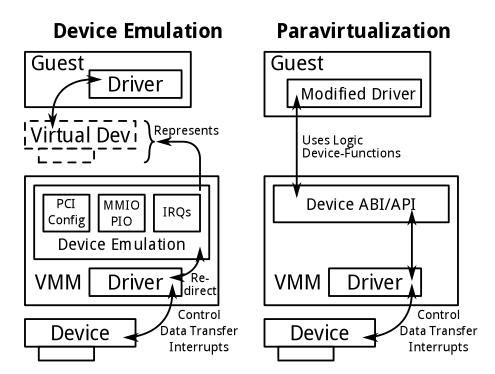

**Emulation and Paravirtualization** Two of the most popular approaches to solve this problem are to completely emulate the devices or to provide a special ABI with logic device function — this this called *Paravirtualization* [AA06, Rus08, Jon10]. An overview for both concepts can be seen in Figure 2.4 on the next page.

Both approaches share that the real device is not exposed in any way to the guests of the VMM, and thus they solve the problem with DMA by not letting the guests access the devices. Instead, the VMM has its own complete device driver and exposes chosen functions of it via a added interface to its guests — how many functions and how they are accessed is based on the chosen method.

**Direct I/O Access via an IOMMU** The downside of both of these approaches is that they require the VMM to implement its own drivers and a device abstraction layer. While this is desirable for VMMs that want to present guests with more resources than actual available or share one resource between multiple guests, it adds unnecessary complexity for others. But to be able to give the guests direct access to the devices, there has to be a mechanism to prevent them from programming the devices with incorrect addresses.

This is the motivation for another extension recently added to x86: *IO Memory Management Units* (abbr. *IOMMU*). The concept behind those is parallel to the

FIGURE 2.4: Diagram showing the architecture of a VMM providing virtualized devices via a software implementation. The left VMM uses a software emulation to provide its guest with an identical interface so it can use an unmodi ed driver. The right VMM provides its guest with a de ned device ABI and API that provides logic functions like <code>send network package</code>; the guest has to use a modi ed driver to use the functions provided by the API with the ABI.

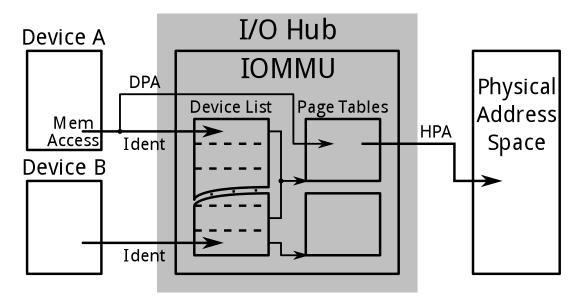

one behind SLAT: an IOMMU adds an address translation step to memory accesses of I/O devices.

Rather than a guest-physical address, the IOMMU introduces the notion of a device-physical address. Those are the addresses the device gets programmed with, and thus whenever the device makes an access via DMA, it will use these addresses, but it won't access the physical memory directly. Once activated, the memory access will be routed through the IOMMU, which is locate between I/O devices and memory — in case of Intel's implementation VT-d, as part of the north bridge [Int13, AJM $^+$ 06].

During the access, the IOMMU will identify the device (for example by its PCI (Bus, Device, Function)-tuple) and select the programmed page table. Each device can have its own page table, or some can share a common one. This table is then used to translate the device-physical address into a host-physical address, which is then used to access the memory.

This setup is, again, programmed by the VMM and transparent to the devices, just as the EPT is to the VMM's guests. The VMM could, for example, decide to map

FIGURE 2.5: Concept of an I/O device making a direct memory access via an immediate IOMMU. *DPA* stands here for *Device-Physical Address* and *HPA* for *Host-Physical Address*. The *Ident* is given implicitly and may for example be the PCI *BDF*.

the exact same memory region in the device's page table, with the same translations, as it does in the EPT. This way, the guest can use its own guest-physical addresses to program the devices, and accesses will translate into the same memory locations for both, and thus relieves the VMM from intervening in this process.

Other than that, VT-d can also be used to handle the device's interrupts (Interrupt Remapping). Again, this is done by applying another translation table. This table is used to redirect interrupts generated by a device to a specific processor, and with that to the guest running on it [Int13]. With this, it prevents inappropriate interrupts to unrelated guests or information leaks.

With both features together and VT-x's ability to moderate accesses to in-memory config areas, it is possible to assign devices directly to a VMM and moderate all the influences guests can have on other parts of the system via DMA or interrupts. It won't however solve all problems that can arise from direct assignment. It is possible that devices employ other communication schemes than DMA, or that a guest brings a device into an unrecoverable fail-state; in both cases it could still violate the control characteristics of the VMM. If such a behaviour is possible for a device, it has to be handled specially  $^1$ .

<sup>&</sup>lt;sup>1</sup>It was not possible to nd a general purpose solution for such a special device behaviour, it is doubtful there is any.

## 2.3 The Jailhouse Hypervisor

Most of the virtualization solutions today make at least use of some of the presented extensions [WP10]. The solutions most commonly known use them to provide a degree of over-provisioning to their users [KNS13]. They aim to run multiple, full operating systems as guests and supply each of these guests with a full range of usable processors and I/O devices. This way, each guest can have its own network adapter, its own set of processors and its own memory. For a VMM running multiple such systems on one physical host, it is hard to provide each of those resources dedicated to only one virtual machine, and thus it is not possible to allow uninterrupted direct access.

To solve this problem, they apply a similar set of algorithms as a normal operating system. Processor time is shared via a scheduler, memory is virtualized via EPTs — interpreting a VM as a normal application running on an operating system, the EPT can be seen as normal page table — and for I/O there is often a mix of emulation and paravirtualization used. Combined, a VMM can allocate a single resource of the host to multiple of its VMs or even over-allocate the resources of the host. If it satisfies the characteristics defined in 2.2 on page 6, the software running on the VMM will not notice anything and won't be able to have influence on others — ignoring impacts in efficiency. While this can increase the efficiency of one host and lower the required physical hosts [KNS13], it also means that it becomes harder to predict what time- and resource-guarantees a VMM can make for its guests [CAA08, CGFC10, XLG+13].

Jailhouse aims for a different goal, it aims to provide its guests with a strong isolation and guaranteed time constraints. Both with only a small and potentially verifiable code base. To make this possible, it doesn't employ *over-provisioning*, any form of scheduling, and resource-sharing only if explicitly configured [Kis14, Sin14a, Sin14b, jaia].

Instead, it splits the available hardware into distinct (static) partitions, and once one of these partitions is allocated to a guest, it is not changed anymore. This approach has already been used in the past on other architectures than x86, for example, IBM's  $System\ z$  provides a similar feature called  $Logical\ Partition$  (abbr. LPAR) [BCDB+14].

To achieve the small code base, Jailhouse refrains from using software to intervene as much as possible. Rather than that, it uses the presented hardware features on x86

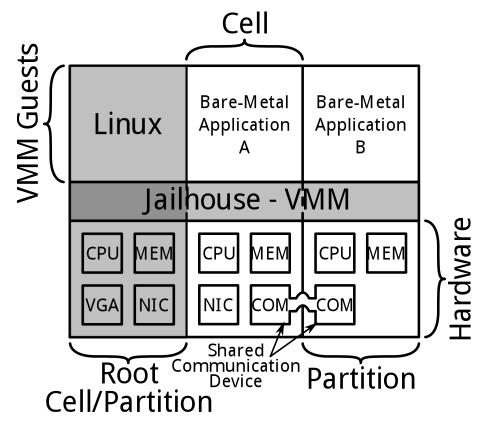

FIGURE 2.6: Overview of Jailhouse's base architecture.

to achieve the isolation, and only traps instructions when absolutely necessary.

**Architecture of Jailhouse** The basic architecture and how Jailhouse organizes a system can be seen in Figure 2.6.

As shown, the available hardware of the system is completely split into separate partitions. One such partition must at least have a single processor and some memory assigned (otherwise, it would not be possible to execute a VM on top of this partition). Other than that, it can be made up from any other available processors, memory and I/O devices. But once a resource is allocated to a specific partition — other than the root partition, which will be explained below —, it is not possible to change or interchange it with a resource from another partition. Otherwise, the user is free to assemble the partitions as he sees fit. He even could explicitly share memory and I/O devices between partitions — although this may be difficult to handle for the guests running on them. The partitions are also frequently called cells in the context of Jailhouse — they are essentially the same as a VM with a static set of resources.

During the start of Jailhouse, the main hypervisor code will be loaded by a Linux

kernel module, alongside with a binary configuration containing a detailed hardware description of the target system — it lists processors, memory and devices, all with their respective access rights. It will then give control to Jailhouse, which will use the given configuration to bootstrap itself on the target machine (it won't use information provided by Linux).

In this bootstrap phase, the VMM will create the *root cell*. This cell will later represent the Linux which started this process. The VMM will assign all CPUs, the memory and all devices to this cell which are described in the given configuration (nothing more, left out resources will not be available). This cell will then finally be programmed with the state of the previously running Linux as guest state, and the VMM will continue running it as guest on top of it (more details of this process will follow later in this section).

Whenever an additional partition is created for another guest, the assigned resources are gradually taken away from the root cell (it is also possible to assign resources to a partition that were not previously assigned to the root cell). The resources will only be given back to it, in case those new partition are destroyed again (if originally configured this way). For most devices — with hotplug functionality — this can be done without modifications to the Linux running in the root cell (there are some corner cases; for example memory is not as easy to handle, the solution for this will be given later in this section)

**Virtualization-Techniques used in Jailhouse** To implement the VMM-functions, Jailhouse makes heavy use of the x86-extensions introduced in this chapter (or equivalent functions on other architectures like ARM). It requires at least a processor with support for VT-x with the EPT-feature and an IOMMU, or the equivalents on AMD's processors.

The guests running in the cells of Jailhouse — this includes the Linux running in the root cell — are executed with the techniques described in 2.2 on page 7. Using the IOMMU, they also get direct access to the allocated I/O devices in their partition. In order to lower the complexity of the hypervisor, Jailhouse tries to not emulate any devices. Exceptions to this rule are parts of the interrupt controller, device configuration spaces, a virtual inter-cell communication-device and interrupt remapping for the root cell.

During the runtime of a non-root guest, Jailhouse tries to do as few VM exits as possible.

The mappings in both the EPT and the IOMMU page table are never change during the runtime of a guest. This means, there will never be page-faults that would require exits and handling (other than page-violations).

Processors are handled in the same way, they are statically assigned to certain guest cells — making scheduling of the them needless. In combination with the interrupt remapping tables of the IOMMU, this makes it also possible to statically assign device-interrupts to certain partitions, which makes exits because of them unnecessary as well.

In general, interrupts only ever cause VM exits, if they could compromise the isolation between the cells (for example, in case of inter-processor interrupts, Jailhouse has to verify that the target processor is in the same cell as the source).

This all makes it possible, unless a guest deliberately accesses sensitive control information, to execute non-Linux guests with zero VM exits.

Other than not emulating any devices, it is also important to note that Jailhouse does not support the *start* of unmodified guests on x86 (Linux can *run* unmodified, if it runs in the root cell). This is because Jailhouse does not emulate a BIOS firmware and has a non-standard reset vector (on x86 this is normally located at 0xFFFFFFFO, Jailhouse places it at 0x000FFFFO)

**Usecases for Jailhouse** It is not the intention of Jailhouse to run multiple full operation systems on one system; this would also be hard to achieve because of the limited resources — multiple full OSs would require a lot of redundant hardware in a machine. The main usecase for Jailhouse are systems that run applications with diverging *criticality* which need to be separated from each other in a safe way.

For example, a system that controls an engine and displays information about it to an operator could be split into two separate cells, one for each task. The engine control, a safety critical task, could run in its own cell and use a dedicated interface card to communicate with the engine (this card would be assigned to the control cell exclusively). The root cell could continue to run Linux and use the existing graphical infrastructure to display the various engine value. It would receive them from the engine control through a defined communication channel. Jailhouse separates both cells in a safe way through the use of the hardware extensions and can thus guarantee that the root cell may never have influence over the engine or the interface card of the control cell. Even if Linux would crash for a reason, this would only let the

uncritical task of displaying the information fail. The engine control could continue to run and safely shut down the engine to react upon the failure of the other cell.

An other field where Jailhouse can be very helpful, is to consolidate legacy single-core operation systems into one multi-core system (e.g.: different RTOSs — no general purpose OSs). Each core of the system, along with a small amount of memory and necessary devices, could execute its own OS and with that continue its lifetime, without the need to re-implement (and possibly re-verify) those tasks in new environments. The Linux in the root cell could then be used as interface to collect and aggregate information of the other OSs, but thanks to Jailhouse it would be unable to influence them inappropriately.

### 2.3.1 Running Jailhouse on Linux

To better understand the later presented solution, to execute Jailhouse in a trusted way, this section will briefly show the key steps of starting Jailhouse in the normal way.

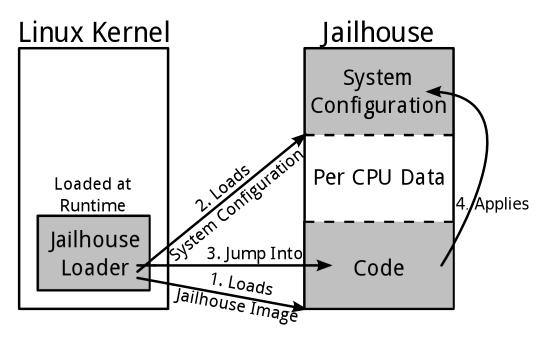

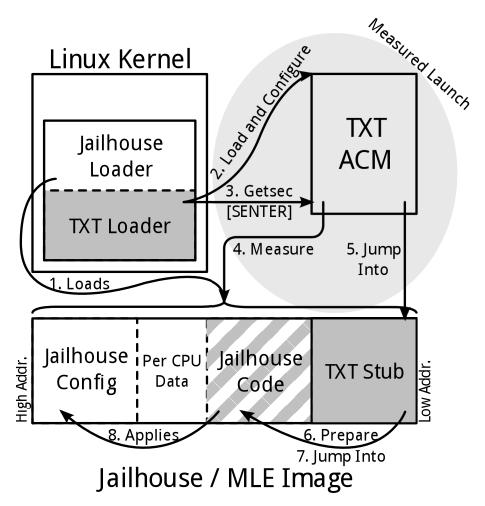

**Jailhouse's Components** An execution of Jailhouse makes use of 4 major software components: the Linux kernel driver, a management utility, the hypervisor image and the hypervisor configuration. An overview of how they interact can be seen in Figure 2.7 on the next page.

Because Jailhouse makes use of VT-x and other hardware extensions, it needs to be executed with privilege level 0 [Int14b] — the highest. Under Linux, this level is restricted to the Kernel and thus the need for a *driver* that runs in the context of the Kernel [Lov10]. Despite that, it is important to note that Jailhouse itself is not part of the Linux Kernel — unlike, for examples, the kernel's own hypervisor KVM [KKL+07]. The kernel is only used to start the hypervisor — to gain the required privilege level, reserve the necessary memory and gain control of all the processors — and to interact with it, once it is started.

The implementation of the driver is also not part of the kernel itself, but also part of Jailhouse and build alongside with it — not as part of, but individual component. The resulting module can be loaded at any time before the start of Jailhouse and will then present the *root* user with a device node as interface (this node is programmed with the usual system calls).

FIGURE 2.7: Diagram showing Jailhouse's software components and how they interact with each other during the startup of the hypervisor.

For the interaction with the driver, a small set of *utilities* is provided along with it. They make use of the provided device-node and are the main user-interface at this point.

The *hypervisor* itself — represented as "Code" in the figure — is represented as a simple binary image. This image is platform specific and only contains the components required for the target system — Intel, AMD, ARM. Which exactly, is decided at compile- and link-time. It does not though contain information about the runtime itself — as for example code location, processor count or available I/O devices.

Those information are stored in the *configuration*. This file will contain a hardware description of the system Jailhouse is executed on (this may contain fewer resources than available; an overview is shown in Table 2.8 on the facing page). Instead of using extensive device- and system- probing via *ACPI*, PCI configuration areas, BIOS or other such methods on x86, Jailhouse relies mostly on its config and applies detection only where it is necessary — for example, to detect runtime information that are to inconstant for long-time storage. As of the moment of this writing, the only exceptions to this, that are taken from Linux, are the logical processor IDs the Linux kernel assigns at its boot-time. These are given as arguments, from the driver to the hypervisor, and are reused as identifier in the hypervisor.

| Configuration Part  | Description                                                                                                                                                                                                                                                      |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hypervisor Location | The (physical) location and size of the hypervisor in the memory during runtime.                                                                                                                                                                                 |

| Processors          | A bitmap enumerating all available processors; the position corresponds to their logical ID.                                                                                                                                                                     |

| Memory Regions      | An exact listing of all memory regions, containing usable RAM and regions reserved for ACPI, PCI and other system components. Each defined region also contains the expected usage permissions (read, write, exec, DMA) and usage type (I/O, comm. region, RAM). |

| IRQ Chips           | A listing of all available IRQ chips and their MMIO location in the memory (e.g. IOAPICs).                                                                                                                                                                       |

| PIO Bitmap          | A description of the whole PIO space with a bit for each port, describing if accesses to this port are allowed or not.                                                                                                                                           |

| PCI Devices         | All available PCI devices, their identifier, type, PCI capabilities and the IOMMU they are behind.                                                                                                                                                               |

| Platform Details    | More details that are specific to the used computer platform, like the amount of available interrupts or number of available IOMMUs.                                                                                                                             |

FIGURE 2.8: Table showing the parts and their description of a Jailhouse con guration le.

**Loading the Hypervisor** Starting Jailhouse, once a complete configuration is created, is straight forward (see figure 2.7 on the preceding page).

Once the driver module is loaded into the Linux Kernel, the root user can enable Jailhouse by sending an IOCTL system call to the created device node, with the chosen configuration as argument. The driver will then map the configured physical hypervisor location into the kernel's page table and load the remaining components into that area (the virtual address space of Jailhouse always start at 0xffffffff0000000). This location is not allocated in Linux, but is reserved for Jailhouse via a boot-time argument of the Linux kernel, and is thus also always at the same location for a given configuration<sup>2</sup>.

The hypervisor image (the code) is loaded at the beginning of the memory area. Following the code, the driver allocates a small amount of memory for each available processor (labeled "per cpu data" in the diagram). This space — seen as simple array — is later used to store information unique to a specific processor. Finally,

<sup>&</sup>lt;sup>2</sup>This may be used at a later point during the development to check the integrity of Jailhouse in safety critical applications, by calculate stable checksum over this area.

the driver loads the given configuration completely and unchanged into the ensuing space.

At this point, all component are loaded into the memory and Jailhouse can be started.

Running Jailhouse To do this, the driver has to make a function call on every available processor into the address space of the loaded code. This function represents the entry-point of the hypervisor and its address is specified at the beginning of the loaded image (in a header). At this point, the hypervisor will only return full control over the hardware back to Linux, in case an error happens during the startup or at the time the hypervisor is shutdown again — the driver relinquishes control over the system on behalf of the Linux kernel.

The entry function will first store all registers which represent the current operation mode and computation state of the kernel, into the area of the particular processor. With those saved states, the VMM will later be able to continue running the Linux as a guest, without any notable discontinuities.

After that, the entry path will continue by checking and promoting Jailhouse's own desired CPU and hardware state, including the change from Linux's page table to a newly created one. This will eventually lead to the setup of the VT-x and IOMMU structures. For this last step, it will put the previously stored processor states into the guest-state area of the VMCS, and its own into the host-state area; and thus, when the VM enter is done, it will continue running Linux as guest with the exact state it had when it entered the entry function.

The lengthly process that happens in between those calls is out of scope of this work; a far more comprehensive description of it can be found in [Sin14a, Sin14b]. Here, we will only note two more points.

First, at the point where the entry function is called, the processors still use the page table of the Linux kernel. Jailhouse will exchange this table for its own and also deploys its own simple page allocator to manage its virtual address space and later on, that of its guests.

Secondly, the EPTs and IOMMU page tables will only contain memory areas specified in the given configuration. That means, if any area is not specified or has the wrong access-permissions, it will not be accessible, neither for the Linux root cell, not for any other cell. The same is applied to the I/O devices of the system: with

a few possible exceptions, only devices listed in the configuration will be mapped with the IOMMU and its interrupt remapping (one exceptions is for example the PM-timer).

Later on, when Jailhouse has returned to Linux as guest, and Linux is used to create other cells, every cell configuration will again state the exact memory areas and I/O devices it wants to use. These are then *removed* from Linux's EPT and IOMMU mappings (if they were present in the original configuration) and hence, become inaccessible for it.

**Metrics About Jailhouse** The size of the hypervisor components and the performance of the presented start procedure can be seen in 6.2 on page 96 and 6.4 on page 99.

# 3 Trusted Execution

At the end of the last chapter, it was shown how important and powerful a single piece of software — the hypervisor — can become. After Jailhouse starts, the whole running software system on the target machine depends on the function of it — even the operating system that executed before it. Even more, the envisioned guests with higher safety requirements than the original operating system will depend on it and on its capabilities to separate them from the other parts of the system. All is concentrated on the proper function of this small, well defined piece of software.

But as of now, there is no way to check whether the loaded hypervisor image is intact and the one that is expected (e.g.: by the user). The only check done is a comparison of a commonly known value in the header of the image. And while this is also often true of other software — operation systems, kernel modules of those, or normal software — the effect of a failure in a hypervisor like Jailhouse is amplified by the type of guests it shall make possible.

This principle can also be observed at other points during the runtime of a computer, and is central motivation for the topic *Trusted Computing* [PMP11] — how can users gain "trust" in the software running on a computer? And while this task covers more, one central problem is to ensure that the expected software was started correctly in the first place and how this can be proven to another party. This subtask is also called *Trusted Boot* or *Trusted Execution*.

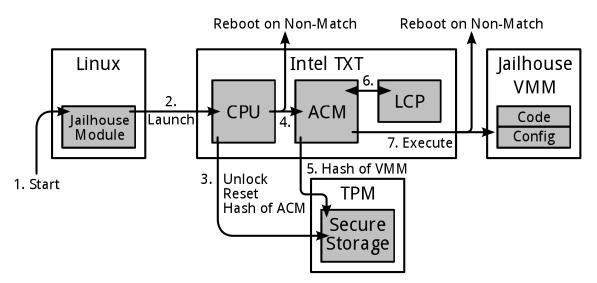

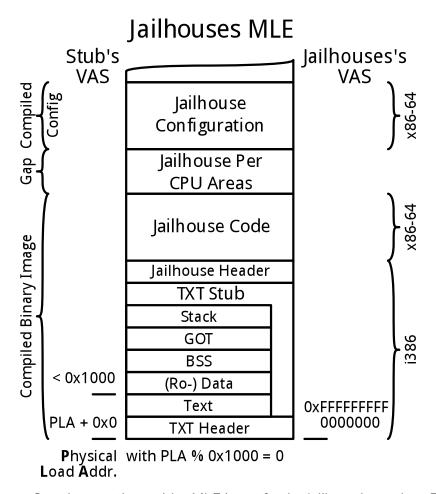

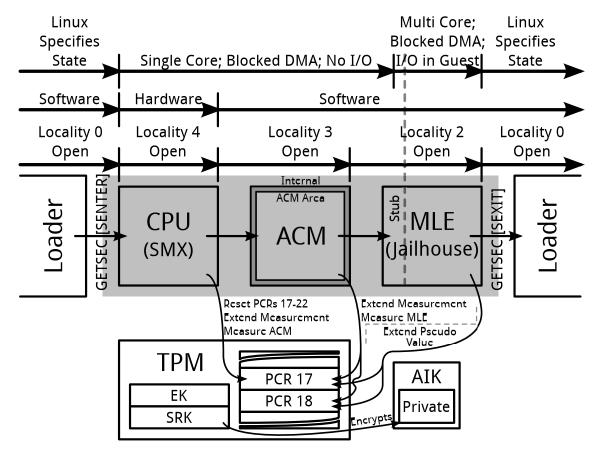

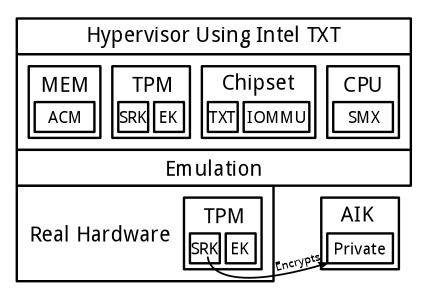

This chapter will give an introduction to this topic and the techniques that are intended to be used to execute Jailhouse in a trusted way. A short, general overview over the envisioned solution will be presented in Section 3.1 on the following page. Section 3.2 on page 27 will define the necessary terms and describe the general techniques to implement Trusted Boot on a modern computer. Section 3.3 on page 32 will then introduce the Trusted Platform Module (abbr. TPM), a hardware extension that is used to support this task. And finally, in Section 3.4 on page 40, the Intel Trusted Execution Technology (abbr. TXT) will be introduced. This is the

FIGURE 3.1: Rough overview over the process of executing the Jailhouse hypervisor in a trusted way, using Intel TXT and a TPM. All the necessary components will be explained in more detail throughout this chapter. A short explanation for the individual steps can be found in section 3.1.

central topic of this work and later it will be evaluate, how TXT can be combined with a hypervisor like Jailhouse.

### 3.1 Overview of the Envisioned Execution

Before going into the details of the trusted execution, this section will give a short overview of the envisioned solution for the hypervisor Jailhouse. The process is visualized in Figure 3.1:

- 1. The start of the process is the same as before: the kernel module receives the signal to start the hypervisor.

- 2. It will then decide to launch the hypervisor with the trusted execution and issue the appropriate commands.

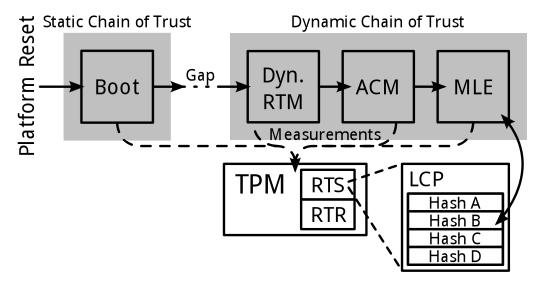

- 3. After that, Intel TXT takes over control of the *whole* system. During this step, the CPU will execute a special procedure outside of user control. It will unlock special functions of the system's TPM (localities; explained later), reset the TPM's secure storage and save a hash of the following software in it (the ACM).

- 4. This saved hash is then compared, and the ACM (software supplied by Intel) only gets to execute if the hash matches an expected value of a cryptographic

signature (this signature is not alterable by the user). Otherwise the CPU will reset the system completely.

- 5. The ACM will then use the unlocked functions of the TPM to save a hash of Jailhouse in the secure storage.

- 6. (optionally) In case the user has (securely) specified in the TPM that LCPs shall be used (a form of hash lists), it becomes required to supply a list of accepted hashed to the ACM (the LCP). Using this, the ACM will search for a hash matching the one of Jailhouse that was just stored.

- 7. Should such a match be necessary and no hash be found, then the ACM will reset the complete system, too. In case no match is necessary, or in case one could be found, it will finally execute Jailhouse.

At each of the transitions (the 4. and 7.) some of the special functions of the TPM are disabled again (privileges, or more precise, localities are lowered). This means amongst other things, the stored hash values can not be reset anymore and any changes to them will show. Related to this, it is also possible for the TPM to unlock secrets based on those hashes — it will only be possible to access the secrets if the correct hashes are computed (this is called *sealing*).

The fact that this process has happened on a target machine can later be proven to other parties. In combination with the LCPs, this will make sure that only good hypervisors will launch.

## 3.2 Establishing Trust in Software

In order to describe how to establish "trust" in software, it is first necessarily to define the relevant terms and their relation to each other.

What is Trust in Software? The term "trust" itself is used in a variety of places and functions. A common definition, when used for software systems and thus also in this work, is given by the RFC 4949 [Shi07]:

**Definition 3.1.** *Trust:* A feeling of certainty (sometimes based on inconclusive evidence) either (a) that the system will not fail or (b) that the system meets its specifications (i.e., the system does what it claims to do and does not perform unwanted functions).

If this definition is applied to the software system in this work — the Jailhouse hypervisor —, it can be narrowed down further. In order to trust the hypervisor's ability to manage its guests in the anticipated way, evidence is necessary that Jailhouse was correctly started and is in control of the virtualization features of the real hardware.

The definition also indicates that this "trust" is not necessarily based on warranties proven for the software system via means like formal verification. To distinguish this more explicitly, the same RFC also defines:

**Definition 3.2.** *Trustworthy*: A system that not only is trusted, but also warrants that trust because the system's behavior can be validated in some convincing way, such as through formal analysis or code review.

So, when this work talks about *trusting a hypervisor*, or more explicitly *trusting in Jailhouse*, it states:

**Definition 3.3.** A third party *trusts* a system to *execute* Jailhouse when given convincing evidence that Jailhouse was successfully started and able to establish its control over the virtualization of the system's hardware.

This also implies that Jailhouse has to be trusted to protect itself from other influences, much like normal operating systems are expected to do the same. Whenever the system in question gives the convincing evidence in question, and the verifier judges it to be correct, then Jailhouse is trusted to be still in control.

But what constitutes such evidence and how can it be provided to a third party in a convincing way?

A common way for this is to provide the *code identity* of the system, and to give a convincing prove that this identity really belongs to the system in question [PMP11].

**Describing the Code Identity of a System** The state-of-the-art method to represent the *Code Identity* of a software is via a *Cryptographic Hash*, taken over the code-binary itself and all its inputs — for normal application this also means all libraries linked into it at runtime. Such a hash Z, computed with a hash function h(x) over the binary and inputs of a software X, is also called *measurement* in the context of this work.

Cryptographic hashes are chosen because they are *Collision Resistant* and *One-Way* [PP10]. With those properties it becomes infeasible hard to calculate a given code identity with another software than the one expected (intentional or unintentional) — it is a very good identity relation.

The best time to take such a measurement is before the software starts to execute. At this point, the hash will always be the same for the same code and input, even across different platforms. For software like an operation system or a hypervisor — software that takes over control of the platform — it is also important that the hash is taken by the software in control before them. Otherwise the measured software might influence the measurement or just lie about it. This in turn raises the question if the software taking the measurement is trusted as well, and to answer this, there has to be a measurement for this software as well.

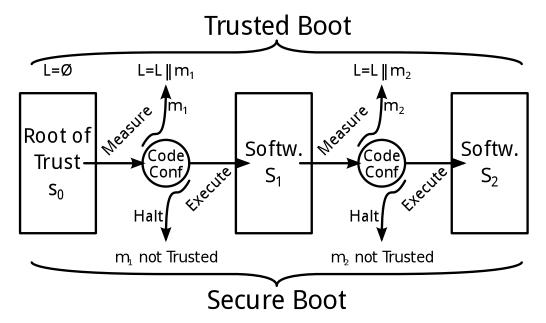

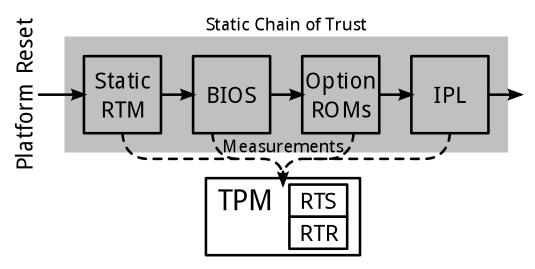

The resulting sequence of measurements L is called *Chain of Trust* [TCG12]. The software currently in control of the system  $S_n$  is measured by its predecessor  $S_{n-1}$ , which in turn is measured by  $S_{n-2}$ . Ultimately though, this sequence has a starting point  $S_0$ , which no matter if it is hardware or software has to be trusted without any more evidence. This start-point is called the *Root of Trust*. If the chain is treated as proof, then the root of trust can be seen as axiom — always true.

An example for this procedure is given in Figure 3.2 on the next page. It also shows two possible applications of how the chain of trust and its measurements can be used: Trusted Boot and Secure Boot [TCG07]. Like established before, the final piece in such a chain has to be trusted to remain in control of the system and to protect itself from being taken over without an additional measurement being made. Depending on the software system, this may also mean that it has to measure every piece of software which can influence it in a untrusted way, so that it could change the trust decision of the trusting parties.

Usually, the involved hardware in this process is also treated as trusted without any further prof. Together with the measurements in L it builds the *Trusted Computing Base* (abbr. TCB) — all the code and hardware that needs to behave in the intended way.

But in order to convince a third party, may it be the user of the computer or an other computer system, that the hardware is currently executing the software system resulting from the shown chain of trust, it is also necessary to find a way to store this information and then to transmit it — both securely.

FIGURE 3.2: Diagram showing a chain of trust and how it is applied in two scenarios:  $Trusted\ Boot$  and  $Secure\ Boot$ . During trusted boot the measurements  $m_X$  are only appended into the chain L. With secure boot they are also compared to a reference value and if they don't match the system is halted.

**Storing the Chain of Trust** When storing the chain of trust L, it has to be made sure that it can't be influenced without being noticed. Any influence at all should be limited to appending new measurements.

Cryptographic hashes can again be used for a part of the problem. The relevant technique is called *Hash Chaining* and is also used in the TPM [TCG07] (later introduce in this chapter). With hash chains, no measurement is stored directly during the computations. Instead, a new measurement is first concatenated with the previous value, and then the result is hashed again. Only then the final value is stored into the "secure location".

Lets assume the root of trust starts with an initial value of

$$L=0$$

:

it then measures the next software with the result  $m_1$ . This value is not stored as such, but instead L is computed as

$$L = h(0 \parallel m_1)$$

;

and only then this value is stored. The measured software is then executed and

repeats this, it measures the next software into  $m_2$  and extends L again as

$$L = h(h(0 \parallel m_1) \parallel m_2)$$

:

This process is repeated till the chain of trust is complete.

Because L is a cryptographic hash, and thus one-way and collision resistant, it is infeasible to find any other combination of softwares, or values in general, that would result in the same hash-value. Not even when the software is execute in a different order:

$$m_1 \neq m_2 \implies h(h(0 \parallel m_1) \parallel m_2) \neq h(h(0 \parallel m_2) \parallel m_1)$$

:

But this still leaves open the problem of finding a "secure location" to store L, so it becomes impossible for any software to just overwrite it or assign a value directly during the hash chain. Both would destroy the chain.

**Convincing a Third Party** After storing L in a secure location, the next problem is to find a way to transmit it to other parties in a convincing way. In particular, the problem is to convince the other parties that the sent hash value L really belongs to the system in question and that it is the value computed and stored in the "secure location".

Convincing another person or system that a message is really from a expected partner is a common problem in cryptography. It is commonly solved by either sharing a secret that only the two communication partners know — symmetric cryptography —, or by asymmetric cryptography [PP10].

In case of asymmetric cryptography, the system in question would use a secret private key to sign the value L before sending both signature and value to the asking party. This system or person has to be in possession of the shared public key which belongs to the just used private key. Using this key, it can verify the received message. Because the private key is only possessed by the trusted party, the messages signed with it can be trusted to contain what is expected, and if they contain a value for L that matches a value of a trusted code identity, the system in question can be trusted to run the corresponding software. Any other outcome, may it be a wrong signature — made with an other private key — or a value for L that not corresponds to a trusted code identity, would lead to mistrust for the asked system.

But this leads to the question: how is the system in question supposed to store the private key, so it will be unknowable to anyone else?

This problem, along with finding the "secure location" to store L, is difficult to solve in software alone. While taking the measurements has been found possible to implement purely in software [GCK05, Spi00], secure storage is still an open issue [PMP11]. The solution is a hardware-based storage and will be introduced in the next section.

#### 3.3 The Trusted Platform Module

The Trusted Platform Module (abbr. TPM) is a hardware module developed by the Trusted Computing Group (abbr. TCG) [TCG07, CYC<sup>+</sup>08, PMP11]. It builds the central piece in the TCG's initiative to specify a common approach for trusted computing, with one target being to support trusted execution. The TPM itself is specified in a platform neutral way [TCG11a, TCG11b, TCG11c] and its implementation for the x86 architecture is specified on its own in [TCG12]. Most of the TPM enabled systems currently in the field are implementing the version 1.2 of the specification; the test system available for this work also ships a chip of this version—the further examination of the TPM is based on this version.

In the context of this work, the primary interest is focused on the TPM's ability to provide the "secure location" to save the chain of trust and its ability to generate verifiable messages from it, in the same manner as described in the previous section.

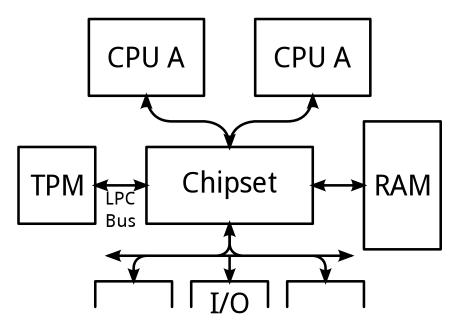

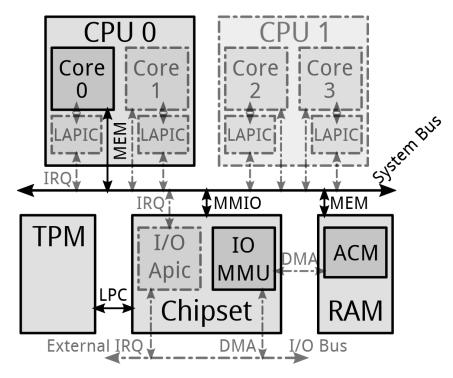

Hardware Integration of the TPM On x86 the TPM is integrated by connecting it via the Low Pin Count Bus (abbr. LPC; specified in [Int02]) to the chipset of the platform [TCG05]. In contrast to other I/O devices connected, it has no ability for DMA or any other direct influence over the behavior of the system — it is completely passive and only ever reacts on requests.

Because the TPM is designed to be inexpensive — one TPM chip costs about one dollar [Cor10] — it does not require much computation power from the chip itself. Timeouts to process single commands are specified from 750ms to up to 2s [TCG05]. The same holds true for the LPC Bus, which transmits a single byte in about 330ns — in comparison to the 20 year old 32 bit PCI bus, clocked with 33Mhz, which

FIGURE 3.3: Overview over the integration of the TPM into the architecture of a x86 platform.

could transmit a byte in about 8*ns*, this is more than a magnitude slower. In general this means that the TPM can not be used to process big amounts of data.

The specification also requires some guarantees against hardware attacks on the TPM chip itself. It terms this as "tamper resistant", more precisely this means that the chip has to be permanently connected to the platform — the motherboard —, so it can not be easily disassembled or transferred to another platform. Attempts of such tampering with the chip shall be evident upon inspection of it [TCG07].

Furthermore, it also requires the TPM packaging to limit attacks like pin probing, to gain knowledge of resident secrets, or electro magnetic scans, as form of side channel attacks to gain information of the functions executing on the TPM. Concerning the LPC bus, which was not designed exactly for this use, the specification only requires it to resist simple attacks and otherwise would need "expertise and possibly special hardware" [TCG11a].

Altogether, it is indicated that this should make it possible to certify a specific TPM implementation according to the FIPS 140–2 standard about cryptographic modules [FIP01], likely up to security level two. At the moment of writing, only one such chip is known and it was only evaluated for security level one [NIS14].

#### Trusted Platform Module NV **PCRs RSA** SHA-1 Ram LPC Communication I/O Bus Exec Key Prg. RNG Engine Code Gen

FIGURE 3.4: Overview of the components of a TPM chip.

#### 3.3.1 Functional Overview

At the core of the functions, the TPM provides are three aspects: secure storage of keys, secure storage for *measurements* and support for trusted reporting. With those, it becomes finally possible to implement a chain of trust as described before. But those are not its only functions, and for this work in particular two more functions will become important: localities and NV RAM. A more detailed overview can be seen in Figure 3.4.

The depicted function blocks correspond to those specified in version 1.2. The implemented cryptographic algorithms in this version are limited to hashing, using the old SHA-1 algorithm (output size is 160 bit), asymmetric cryptography (including signing), using RSA with keys up to 2048 bits, and an own Random Number Generator with its own source for entropy. And although there is some non-volatile memory available on the chip, the specification only requires it to be 1280 byte big [TCG05].

**Secure Storage of Measurements** Like previously explained (3.2 on page 30), it is important to have a secure location to store measurements during the build of the chain of trust.

Because the TPM has only a very limited amount of storage available, it solves this problem with the  $Hash\ Chaining\ algorithm\ explained$  in the same section. To store the hashes, it provides 24 so called  $Platform\ Configuration\ Registers\ (abbr.\ PCR)$ . These registers are volatile, but mostly only reset during platform resets (the

registers with the indices 16 to 23 can be reset during the runtime, using the *locality* mechanism explained in 3.3.1 on page 38). Additionally, values can never be written directly, but they are always concatenated with the previous value and then hashed again — just as explained (the command is called TPM\_Extend).

The PCRs with indices from zero to 15 (also called *static PCRs*) are used during the boot phase of the system (explained in 3.3.1 on page 37). They store information like the hash of the used BIOS, option ROMs, the used IPL, loaded OS, and for each the used configuration. Those can not be reset during the runtime and will reset during platform reset to zero. The remaining PCRs 16 to 23 (called *dynamic*) will be explained later.

Secure Storage for Keys The next problem is how a system can store private keys in a secure location, over a potentially very long time frame. Because of the limited amount of non-volatile RAM, storing them on the TPM directly is not a good option. Instead, the TPM is used to encrypt the private portion of such a asymmetric key or, in case of symmetric cryptography, the whole key. And once encrypted, the TPM will only decrypt them again in case a good authentication is given — this could be a pass phrase, a specific value stored in a set of PCRs, or the activation of a high enough locality. But again, for this operation it also needs a secret key (a RSA key in the case of the TPM)!

There are two (RSA-) keys permanently stored on the TPM: the *Endorsement Key* (abbr. EK) and the *Storage Root Key* (abbr. SRK).

The **EK** is stored on the TPM by the manufacturer and can never be changed. It is the TPM's identity and because the TPM is permanently connected to the platform, it is the identity of that, too. Because this intimate relationship can result in privacy issues, in case the public portion of the EK is used to permissive, its function is restricted to signing certificates of other keys (they are called AIK; further explanations will follow), stating: "this key belongs to the TPM with this EK". With the help of an external agency, the owner of the TPM can then request a second certificate for this new key, stating: "this key belongs to a trusted TPM"; and has thus decoupled the AIK from the EK. Ideally, there would also be a certificate stored on the TPM that attests that the EK belongs to a confirming TPM chip, signed by a similar agency, but this optional idea of the specification never prevailed [PMP11].

The **SRK** is created during the establishment of the TPM's ownership. Initially, the TPM is in an "unowned" state and the user has to first take ownership over it

(TPM\_TakeOwnership). This process establishes a shared secret between the owner and the TPM (likely a password), and creates the SRK. Whenever the ownership is revoked (requires the secret) this key is removed as well.

The private parts of both keys never leave the TPM, not encrypted, and in no other circumstance, they are only used in operations on the TPM (the public parts can be retrieved).

When an other key is generated on the TPM, then its private part, together with other information, is encrypted with the public key of the SRK. Only then it is allowed to leave the TPM. This technique is called *binding* or *wrapping*. And because those bound keys are encrypted with the public part of the SRK and the corresponding private part never leaves the TPM, they only ever can be used inside that specific TPM<sup>1</sup> (because of this, the SRK is also called to *Root of Trust for Storage* (abbr. *RTS*)).

Next to the binding, it is also possible to specify additional criteria for decrypting or using such keys: it is possible to specify a password; it is possible to specify a set of PCRs, and only if those PCRs have the value, as at the time the key was created, the key becomes usable (also called *sealing*, security is based on the collision resistance of the hashes); and finally it is possible to specify a locality that has to be satisfied.

Next to normal RSA keys, the TPM also provides some that have a special meaning for it. One important kind are Attestation Identity Keys (abbr. AIK), RSA keys that are only used to sign information and with that, attest that those information belong to the TPM to which the AIK is bound. They are created and bound directly to the SRK of the TPM in question. The information that they are for this special purpose is encrypted along with the private part of the key. As an option, they can also be certified with the EK's certificate as parent (as described before), if there was one created for it<sup>2</sup>.

**Trusted Reporting** With those two aspects solved, it is possible to construct a way to send convincing evidence to users or other computers about the code identity of

<sup>&</sup>lt;sup>1</sup>It is also possible to create migratable keys or encrypt/decrypt arbitrary data, but this is out of context for this work.

<sup>2</sup>It is, of course, also possible to create a private certicate chain, using the public key of the EK and the public keys of the AIKs, but for this work it is succient to know the public portion of the key.

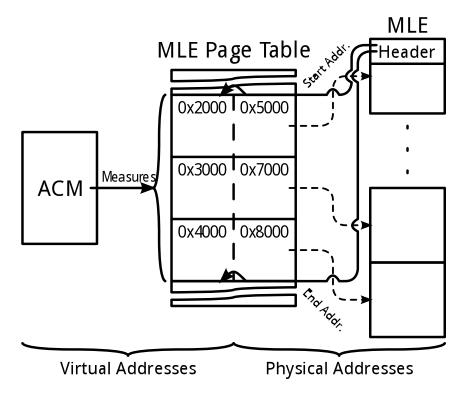

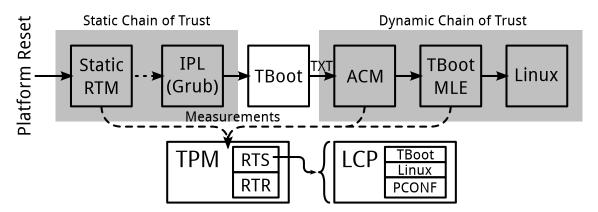

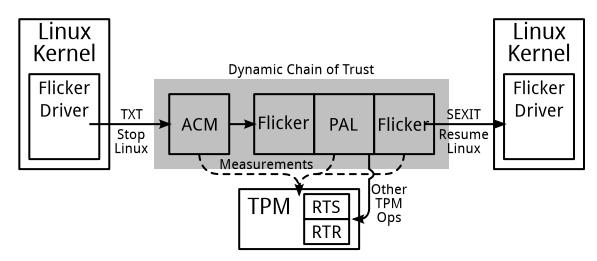

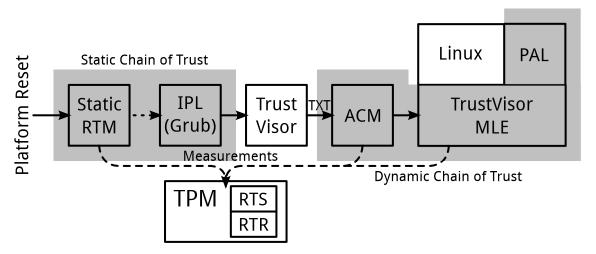

the platform. For this, the TPM provides a specific command: TPM\_Quote; and calls this procedure *Remote Attestation*.